## AF430/HSM Instruction Manual

DTS INSIGHT CORPORATION.

AF430/HSM Instruction Manual No. M2383MW-01

# **Publication History**

| Edition Date of Issue |                   | Description         |

|-----------------------|-------------------|---------------------|

| 1st edition           | 29 February, 2016 | Initial publication |

|                       |                   |                     |

# <Contents>

| 1. | Ove  | erviw                                                              | 3  |

|----|------|--------------------------------------------------------------------|----|

| 1  | .1.  | Part Names and Functions                                           | 4  |

| 1  | .2.  | External configuration & dimensions of the Adapter area            | 8  |

|    | 1.2. | .1. Connector(EXT PROBE1/AZ773-NET IMPRESS-side)                   | 8  |

|    | 1.2. | .2. Interface Cable (AZ770)                                        | 8  |

|    | 1.2. | .3. Signal Table (EXT PROBE1/AZ773-NET IMPRESS-side)               | 9  |

| 1  | .3.  | TARGET PROBE                                                       | 10 |

| 2. | Tar  | get Interface                                                      | 11 |

| 2  | .1.  | Signal and pin assignment                                          | 11 |

| 2  | .2.  | Circuit Specification                                              | 12 |

| 2  | .3.  | Pin assignment of the target side                                  | 13 |

| 3. | DC   | Characteristics                                                    | 15 |

| 4. | AC   | Characteristics                                                    | 16 |

| 4  | .1.  | Clock Timing                                                       | 16 |

| 4  | .2.  | Signal Timing (as seen from the adapter side)                      | 16 |

|    | 4.2. | .1. A target system which TDO is output on the falling edge of TCK | 16 |

| 5. | Coi  | nnecting a Target System                                           | 17 |

## 1. Overview

AF430/HSM (NETIMPRESS next) supports programming flash ROM of a microcomputer on a user system using JTAG protocol by connecting the optional adapter.

\*\*Refer to NETIMPRESS next Users Manual for further details.

(Manual is available from our home page. Download them from the link below.)

https://www.dts-insight.co.jp/en/support/support\_netimpress/top/index.php?m=Hardware

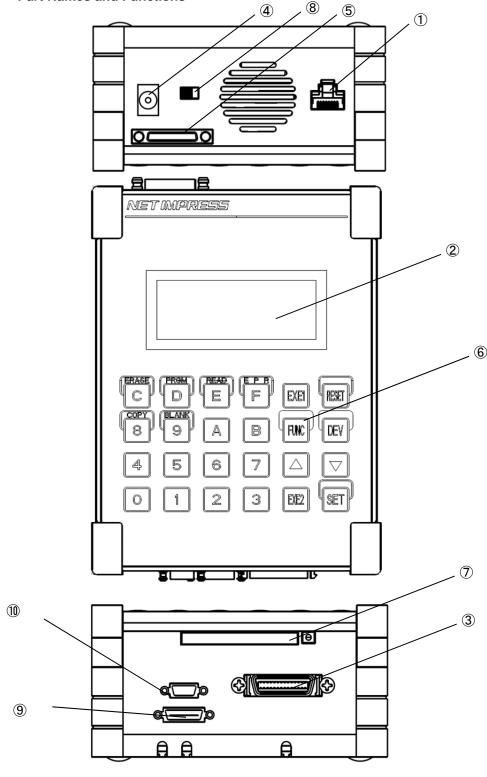

## 1.1. Part Names and Functions

## **1** ETHERNET

This is the connector to connect with Ethernet (10/100Base-T).

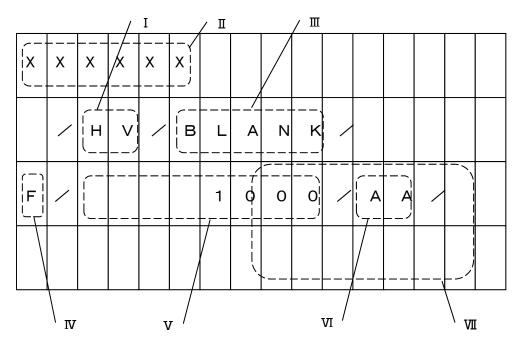

## ② LCD

Displays various information.

## I. Programming power application display

This shows that high voltage power for programming is being applied. This display can be cleared by pressing the RESET key.

## II. Type of the target Micom

Displays type of the target Micom.

## III. Device function display

Displays the device function being executed.

## IV. Function display/Modify bit display

Displays the function currently being executed or that the data in the buffer memory is modified data.

When "F" is displayed, it indicates the function, which is currently being executed.

When "D" is displayed, it indicates the device function, which is currently being executed.

When "M" is displayed, it indicates the data modified by the key entry or buffer transfer

## V. Address display

Displays the flash memory address, data key entry and various messages. This only displays the lowest eight address digits and does not display the higher address digits.

#### VI. buffer memory data /error codes

Displays buffer memory data and error codes.

#### VII. ROM data/sum check

Displays the flash ROM data and a sum value of buffer memory data.

## **③ TARGET PROBE1**

This is the connector to connect the probe that connects with a target system.

#### **4** DC12V

This jack is to connect the AC adapter for NETIMPRESS next.

#### **⑤** DIO PROBE

This is the connector to control by digital I/O.

#### **6** KEYBOARD

#### [ 0~F ]

Use the hexadecimal data keys to enter the numeric values. 8, 9, C, D, E and F are used as the keys to specify each device function combining with the DEV key.

#### [ RESET ]

Use this key to abort operations or delete the error messages. Pressing this RESET key disconnects remote connection too.

#### [ FUNC, DEV ]

Use these command keys to make various operation settings combining with the hexadecimal data keys.

## [ ▲ ▼ ]

These are the keys to increment and decrement the address values. The buffer memory and the ROM data for the addresses are displayed simultaneously. This is also used as a parameter delimiter for FUNC.

#### [ SET ]

Use this key to set the functions and device functions. You can also use this SET key to modify the data in buffer memory.

#### 【EXE1, EXE2】

You can assign various commands to these two keys. For further information, see Chapter 6 "Command Sequence Function".

## **⑦** CONTROL MODULE

This is the slot to insert the control module. NETIMPRESS next only operates with its specific Compact Flash.

## **8** Power Switch

I: Power ON

O: Power OFF

## **9** EXT PROBE1

This connector is used to connect a probe to connect AZ773 JTAG adaptor and a target system.

## **10** BCR PROBE

This is the connector to connect the probe that connects with a bar-code reader.

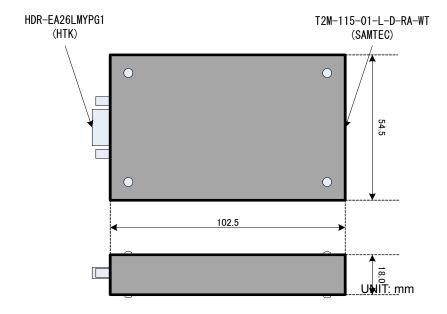

## 1.2. External configuration & dimensions of the Adapter area

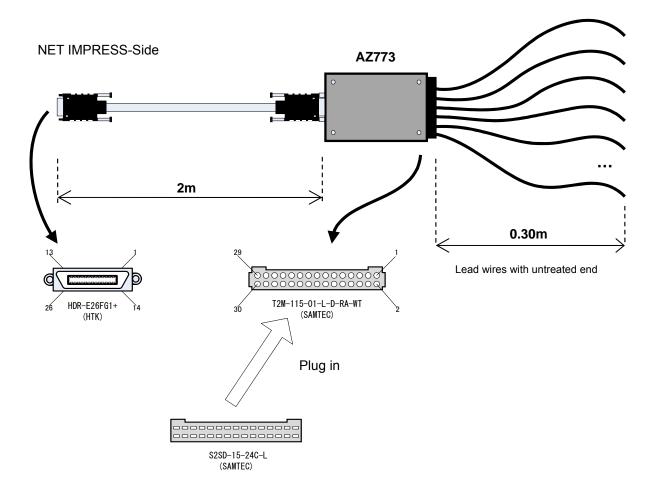

The figure below illustrates external configuration and dimensions of the adapter area of AZ773.

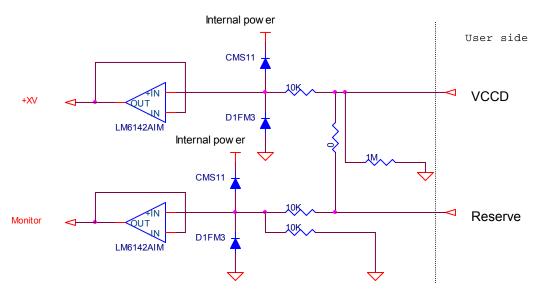

## 1.2.1. **Connector** (EXT PROBE1/AZ773-NET IMPRESS-side)

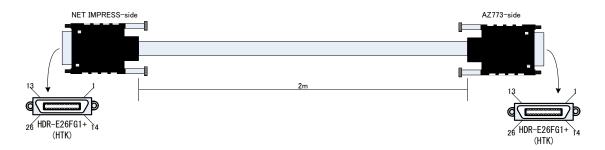

## 1.2.2. Interface Cable (AZ770)

This cable is used to connect NET IMPRESS and AZ773 adaptor.

## 1.2.3. Signal Table (EXT PROBE1/AZ773-NET IMPRESS-side)

| No. | Signal<br>Name | Meaning                              |   |

|-----|----------------|--------------------------------------|---|

| 1   | RSV2           | Reserve 2(STATUS2)                   |   |

| 14  | RSV1           | Reserve 1(STATUS1)                   | I |

| 2   | SEL            | L=Normal operation、H=Version up mode | 0 |

| 15  | SDI            | SPI data input                       | I |

| 3   | SDO            | SPI data output                      | 0 |

| 16  | SCS            | SPI select output                    | 0 |

| 4   | SCK            | SPI clock output                     | 0 |

| 17  | VCC            | ADP power source                     | - |

| 5   | VCC            | ADP power source                     | - |

| 18  | VCC            | ADP power source                     | - |

| 6   | VCC            | ADP power source                     | - |

| 19  | GND            | GND                                  | - |

| 7   | RXD-           | Receive data input (-)               |   |

| 20  | RXD+           | Receive data input (+)               | I |

| 8   | GND            | GND                                  | - |

| 21  | GND            | GND                                  | - |

| 9   | RXC+           | Receive clock input (+)              |   |

| 22  | RXC-           | Receive clock input (-)              | I |

| 10  | GND            | GND                                  | - |

| 23  | GND            | GND                                  | - |

| 11  | TXD-           | Send data output(-)                  | 0 |

| 24  | TXD+           | Send data output (+)                 | 0 |

| 12  | GND            | GND                                  | - |

| 25  | GND            | GND                                  | - |

| 13  | TXC+           | Send clock output (+)                | 0 |

| 26  | TXC-           | Send clock output (-)                | 0 |

<sup>\*1、</sup>O:OUT(NET IMPRESS→AZ773)、I:IN(NET IMPRESS←AZ773)

## 1.3. TARGET PROBE

Pin layout of each connector is numbered as viewed from the mating side.

## 2. Target Interface

## 2.1. Signal and pin assignment

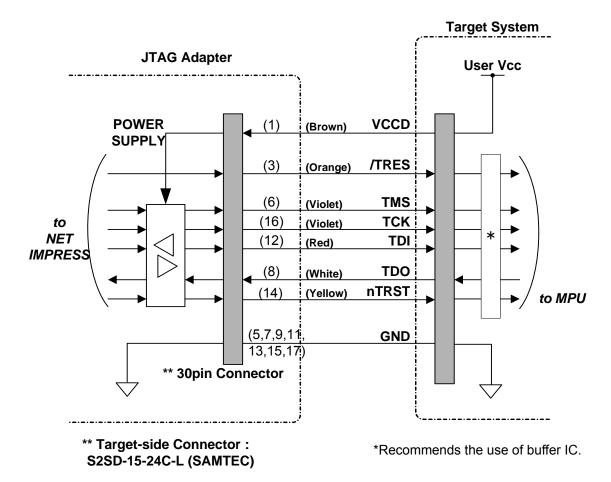

The table below lists signals of AZ773 JTAG adapter at user target side. I/O (Input and Output) information is for AZ773.

| Signal Name | Meaning                                                                                    | I/O    | Туре |

|-------------|--------------------------------------------------------------------------------------------|--------|------|

| VCCD        | Power input from user target to AZ773 Used as buffer power source for I/O signals of AZ773 | I      | Α    |

| Reserve     | Reserved signal. Do not connect any signal at target side.                                 | _      | В    |

| /TRES *1    | Negative logic reset output (Open collector output)                                        | 0      | С    |

| /WDT *1     | Watchdog timer output (Open collector output)                                              | 0      | O    |

| IO1(TMS)    | (JTAG TMS output)                                                                          | I/O(O) | D    |

| IO2(TDO)    | (JTAG data input)                                                                          | I/O(I) | D    |

| IO3         | Connect as needed only.                                                                    | I/O    | D    |

| IO4(TDI)    | (JTAG data output.)                                                                        | I/O(O) | D    |

| IO5(nTRST)  | (JTAG nTRST output.)                                                                       | I/O(O) | D    |

| IO6(TCK)    | (JTAG TCK output.)                                                                         | I/O(O) | D    |

| IO7~IO16    | Connect as needed only.                                                                    | I/O    | D    |

| NC          | Not connected                                                                              | _      | _    |

| GND         | Connect with GND at target side.                                                           | _      | _    |

<sup>\*1 /</sup>TRES,/WDT are open collector output. Please implement the pull-up resistor to the target side.

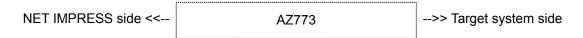

## 2.2. Circuit Specification

Type A, B

Type C

User side

/TRES、/WDT

Type D

\*\*XV

LVC

User side

IO1~IO16

\*\*+XV can be used as an interface power supply to equal the signal level with target system.

## 2.3. Pin assignment of the target side

The table below lists pin assignment of the connector of AZ773 at the target side.

| Pin No. | Lead Color | AZ773 Signal Name | I/O |

|---------|------------|-------------------|-----|

| 1       | Brown      | VCCD              | I   |

| 2       | Red        | Reserve           | -   |

| 3       | Orange     | /TRES             | 0   |

| 4       | Yellow     | /WDT              | 0   |

| 5       | Green      | GND               | -   |

| 6       | Violet     | IO1               | I/O |

| 7       | Grey       | GND               | -   |

| 8       | White      | IO2               | I/O |

| 9       | Black      | GND               | -   |

| 10      | Blue       | 103               | I/O |

| 11      | Brown      | GND               | -   |

| 12      | Red        | 104               | I/O |

| 13      | Orange     | GND               | -   |

| 14      | Yellow     | 105               | I/O |

| 15      | Green      | GND               | -   |

| 16      | Violet     | 106               | I/O |

| 17      | Grey       | GND               | -   |

| 18      | White      | 107               | I/O |

| 19      | Black      | 108               | I/O |

| 20      | Blue       | 109               | I/O |

| 21      | Brown      | IO10              | I/O |

| 22      | Red        | IO11              | I/O |

| 23      | Orange     | IO12              | I/O |

| 24      | Yellow     | IO13              | I/O |

| 25      | Green      | IO14              | I/O |

| 26      | Violet     | IO15              | I/O |

| 27      | Grey       | IO16              | I/O |

| 28      | White      | NC                | -   |

| 29      | Black      | NC                | -   |

| 30      | Blue       | NC                | -   |

XI/O listed in the table above indicates input and output from the adapter to a target system.

<sup>\*\*</sup>The above listed GNDs (5,7,9,11,13,15 and 17) are common with each other in the adapter.

Connect as many GNDs as possible to a target system for stable electric connection.

\*Be sure that untreated signal wires at the target side do not short out with other signal wires or metal parts of test pins, for example.

## 3. DC Characteristics

Listed +XV below are power supply voltage for I/O buffer, which are generated from VCCD. Output voltages vary affected by voltage drop by serial resistances in the adapter and input circuit on a target system.

| Signal   | Item              |      |            | Min             | Max       | Unit      |    |

|----------|-------------------|------|------------|-----------------|-----------|-----------|----|

|          | Input             | Vin  |            | Absolute rating | -0.3      | 5.25      | V  |

| VCCD     | voltage           |      |            | Operate range   | 2.0       | 5.0       |    |

|          | Input<br>current  | lin  |            | _               | _         | 263       | uA |

| /TRES    | Input<br>voltage  | Vin  |            | Absolute rating | -         | 7.0       | V  |

| /WDT     | Output voltage    | VoL  | Isink=-3mA | _               | 1         | 0.7       | V  |

|          |                   |      | IoH=-8mA   | +XV=2.3V        | 1.9       | _         | V  |

|          |                   | VoH  | IoH=-24mA  | +XV=3.0V        | 2.4       | -         |    |

|          | Output<br>voltage |      | IoH=-32mA  | +XV=4.5V        | 3.8       | _         |    |

|          |                   | VoL  | IoL=8mA    | +XV=2.3V        | 1         | 0.3       |    |

|          |                   |      | IoL=24mA   | +XV=3.0V        | 1         | 0.55      |    |

|          |                   |      | IoL=32mA   | +XV=4.5V        | I         | 0.55      |    |

|          | Output<br>current |      |            | +XV=2.3to2.7V   | 1         | ±8        | mA |

|          |                   | lout |            | +XV=3to3.6V     | 1         | ±24       |    |

| IO1~IO16 |                   |      |            | +XV=4.5to5.0V   | I         | ±32       |    |

|          | Input<br>voltage  |      |            | +XV=2.3to2.7V   | 1.7       | -         | V  |

|          |                   | ViH  |            | +XV=3to3.6V     | 2.0       | -         |    |

|          |                   |      |            | +XV=4.5to5.0V   | +XV x 0.7 | -         |    |

|          |                   | ViL  |            | +XV=2.3to2.7V   | 1         | 0.7       |    |

|          |                   | VIL  |            | +XV=3to3.6V     | 1         | 0.8       |    |

|          |                   |      |            | +XV=4.5to5.0V   | _         | +XV x 0.3 |    |

|          | Input<br>current  | lin  |            | _               | _         | 12        | uA |

<sup>※/</sup>TRES,/WDT are open collector output.

## 4. AC Characteristics

## 4.1. Clock Timing

| Signal   | Item                | Min   | Max   | Unit |

|----------|---------------------|-------|-------|------|

| IO6(TCK) | Operating frequency | 1.25M | 10.0M | Hz   |

## 4.2. Signal Timing (as seen from the adapter side)

This section describes AC timings under conditions below.

Vccd input (Voltage of target system): 3.3 V

Cable between NETIMPRESS and AZ773: AZ770 (2 m) \*Our standard

Cable between AZ773 and a target system: 0.30 m long untreated wires \*Our standard

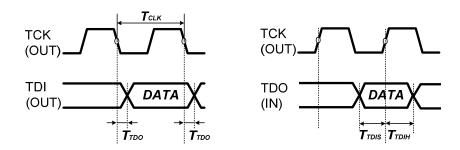

## 4.2.1. A target system which TDO is output on the falling edge of TCK

| Symbol            | Item                                                  | Characteristic                               | Condition                           |

|-------------------|-------------------------------------------------------|----------------------------------------------|-------------------------------------|

| T <sub>TDO</sub>  | Delay time from the falling edge of TCK to TDI output | Max. 16ns                                    | Independent on JTAG clock frequency |

| T <sub>CLK</sub>  | TCK cycle time                                        | Min. 100ns                                   | TCK=10MHz                           |

| T <sub>TDIS</sub> | Setup time for TDO to the rising edge of TCK          | Min. 0ns                                     | Independent on JTAG clock frequency |

| T <sub>TDIH</sub> | TDO hold time after the rising edge of TCK            | Min. T <sub>CLK</sub> (TCK cycle time) ÷4 ns | 25ns (TCK=10MHzOperation)           |

## 5. Connecting a Target System

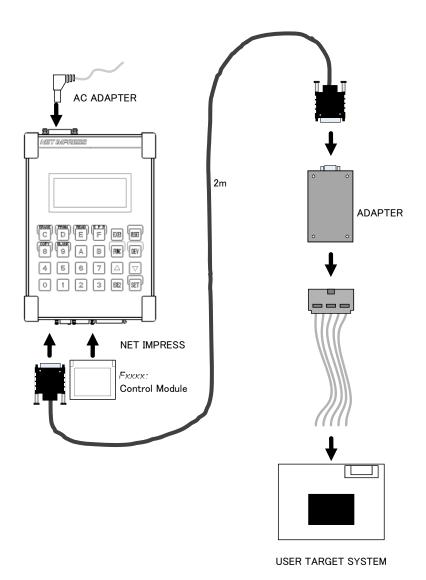

The figure below illustrates how NET IMPRESS, AZ773 and a user target system are connected.

The figure below illustrates the example of connection on a circuit.

See the NETIMPRESS Instruction Manual when connecting NETIMPRESS' original signals other than signals commonly used in JTAG communication.

For the signal lines not used, you can leave them open unless otherwise specified in the Control Module Instruction Manual.